## UNIVERSITY OF RUHUNA

## BACHELOR OF SCIENCE (GENERAL) DEGREE LEVEL II (SEMESTER I) EXAMINATION- JULY 2016

SUBJECT :

COMPUTER SCIENCE

**COURSE UNIT**

: COM 2141 (Computer Architecture)

**DURATION: 1 Hour**

## Answer Two (02) questions.

1.

a.

- Convert 7459.56<sub>10</sub> to octal equivalent. Limit your answer to five fractional digits. [10 marks]

- ii. Convert 1678.58 to binary and hexadecimal equivalents.

[10 marks]

iii. Solve the following problem. Clearly show the steps you follow.

[6 marks]

- 111011<sub>2</sub> × 101<sub>2</sub>

- iv. Convert 111101112, which is written in two's complement notation, into the decimal equivalent [10 marks]

- v. Using 8-bit two's-complement notation, solve the mathematical calculation: (-64-98). Explain whether any register overflow exist or not in this operation. [20 marks]

. b.

ax

- i. Explain why spatial locality is important in memory access using an example. [12 marks]

- ii. Write down three main technological factors that are required to determine the capacity of a hard disk. [12 marks]

- iii. Explain why cache memory is important for the operation of the central processing unit. [10 marks]

- iv. Explain why you agree or disagree with the following statement using two technological factors: "DVD have higher capacity than blue ray disks".

[10 marks]

a.

i. Prove that NOR is an universal gate using logic circuit diagrams.

[10 marks]

ii. Simplify the following expression, by using Boolean algebraic postulates and theorems. (A+B). (A'+C). (B+C). Clearly indicate the steps and theorems you apply.

[15 marks]

b.

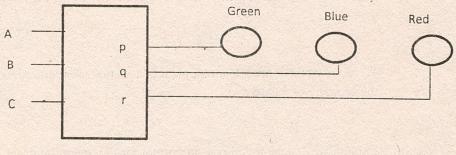

Three indicator lights of red, green and blue are used to show the progress level of a manufacturing process as shown in Figure 1. Assume that there are eight main stages of the manufacturing process. The output stage of the manufacturing process which is given by a decimal number  $(0,1,2,3,\ldots,7)$  is input to the combinational circuit using 3 inputs: A, B and C as the equivalent binary number of three digits (representation  $(0_{10}=000,\ldots,3_{10}=101,\ldots,7_{10}=111)$ ). Green indicator light is lit only when the process is in  $0^{th}$ ,  $1^{st}$ ,  $2^{nd}$  output stages of manufacturing. Blue indicator light is lit only when the process happens in the  $3^{rd}$  and  $4^{th}$  stages. Red indicator light is lit only when the process is in the final  $5^{th}$ ,  $6^{th}$  and  $7^{th}$  stages. The three outputs (p, q, r) define which lights will be lit to indicate the progress of the process.

Figure 1

i. Develop a truth table for the three inputs (A, B, C) and three outputs (p, q, r) of this circuit to display the progress level. [15 marks]

ii. Express outputs 'p', 'q' in sum of products form. [10 marks]

iii. Express the output 'r' in product of sums form. [5 marks]

iv. Simplify the expression you wrote for 'p' using k-maps. [20 marks]

v. Design a logic circuit to implement the simplified sum-of-products expression for 'p' obtained in above 2) b) iv) by using **NAND gates**. Clearly indicate the method and steps you follow. [25 marks]

a.

3.

- i. Prove that a full adder can be used to add three binary bits by using a truth 'table. [15 marks]

- ii. Explain the five main steps which are followed in the process of executing a stored instruction by the central processing unit.

[20 marks]

iii. Assume that a central processing unit (CPU) employs a memory address register (MAR), a memory buffer register (MBR), a program counter (PC), and an instruction register (IR) as following. Explain how data flows during the instruction fetch cycle.

[20 marks]

iv. Write down 4 possible elements that can be found in a machine instruction. [8 marks]

b.

- i. Name the stages of instruction execution in a six stage pipeline. [12 marks]

- ii. Assume that an instruction is stored in memory at address 100. The address field has the value of 200. The content of memory address 200 is 300. The program counter has the value 100 for fetching this instruction. The content of processor register R is 500, and the content of an index register is 80. Evaluate the effective address for each of the following addressing modes. [25 marks]

- a. Direct

- b. Indirect

- c. Register indirect

- d. Relative

- e. Indexed