## UNIVERSITY OF RUHUNA

## Faculty of Engineering

End-Semester 5 Examination in Engineering: December 2020

Module Number: EE5201 Module Name: Computer Architecture

[Answer all questions, each question carries 12.5 marks]

[Three Hours]

- 0 a First generation computers used vacuum tube technology.

- respectively. State two other technologies used by second and third generation computers,

[1 Mark]

E State two input/output technologies used by first generation computers

[1 Mark]

9 1 State two limitations in increasing the clock speed of microprocessors

11)

- State three different bus hierarchies designed to improve the system performance. [1 Mark]

- [1 Mark]

- Ei) Compare the single-core architecture with multi-core architecture

[2 Marks]

- 0 i) State what is meant by cycles per instruction (CPI).

- calculate the CPI. instructions each taking 4 clock cycles, and 10 instructions each taking 10 clock cycles Suppose that a processor executes 25 instructions each taking 5 clock cycles, 65 [1 Mark]

- [1.5 Marks]

- E T) State what is meant by State two techniques built into the processor to improve the performance. the Speedup of a computer with respect to parallel [1 Mark]

0)

processing.

iii) Suppose that a program with 20% instructions that cannot be executed in parallel is run on a computer with 10 parallel processors. Calculate the speedup that the computer can achieve? [1 Mark]

[2 Marks]

|        | 5                                                         |

|--------|-----------------------------------------------------------|

|        | a                                                         |

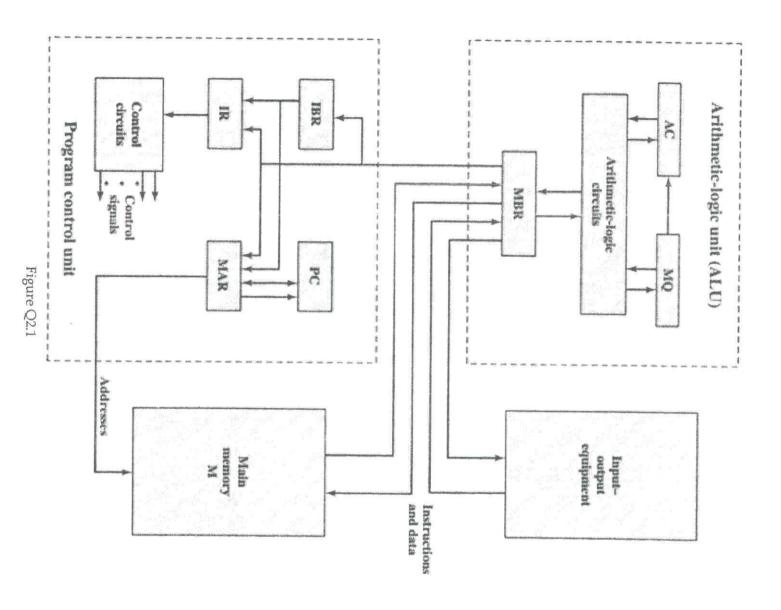

| <br>i) | Figure<br>function                                        |

| PC     | e Q2.1 shows a block diagram onality of following blocks. |

|        | of t                                                      |

|        | f the \                                                   |

|        | Von                                                       |

|        | Neumann                                                   |

|        | architecture.                                             |

|        | State                                                     |

|        | the                                                       |

R

H) MAR

iv) MBR

IBR

5

$[0.5 \times 5 = 2.5 \text{ Marks}]$

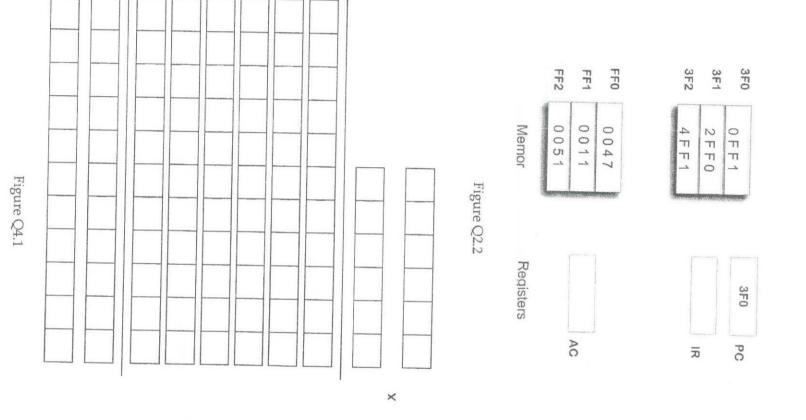

9 Consider the hypothetical machine explained below Instruction length: 16 bit

Instruction format: Four most significant bits represent the opcode rest represent

List of instructions:

0x00 Load AC from memory

0x01 Store AC to memory

0x02 Add AC from memory

0x04 Add AC to memory

0x08 Clear AC

executing following. given state. Identify the changes to any of the given registers / memory location after Snapshot of the machine shown in Figure Q2.2. Machine will start its operation from the

-First instruction.

E Second Instruction

[2 Marks]

III) Third instruction.

[2 Marks]

[2 Marks]

0 J) State three key stages of the instruction cycle.

[1 Mark]

ii) Use a block diagram to explain how an interrupt affects the instruction cycle.

having the same priority. interrupt service routines when interrupts are with different priorities and all interrupts Consider an architecture with multiple interrupts. Compare the difference between [1 Mark]

[2 Marks]

03 a) 1 State two performance parameters of memory

E)

- respect to the access times of different memory locations. State the difference between Random access and Sequential access memory, with [1 Mark]

- [1 Mark]

- III) State the difference between DRAM and SRAM.

[1 Mark]

iv) State three cache mapping schemes

6

1)

this system.  $\mu$ s and access time of the main memory is 1  $\mu$ s. Evaluate average memory access time of A processor consists of level 1 (L1) cache with a hit-ratio of 0.9 and access time 0.01 [1.5 Marks

access time is 0.1  $\mu$ s. Evaluate average memory access time of the system with L1 cache, cache in between L1 cache and the main memory. The hit-ratio of L2 cache is 0.95 and the L2 cache, and the main memory. Assume that the next version of the processor architecture inserts a level 2 (L2) 2 Marks

[Hint: Sketch two levels of cache and the main memory and work out the probabilities] [2 Marks]

0 Assume that an 8-bit data packet is encoded using Hamming codes and stored in the memory. Hamming bits used in encoding are given by

$P2 = D3 \oplus D6 \oplus D7 \oplus D10 \oplus D11$  $P4 = D5 \oplus D6 \oplus D7 \oplus D12$  $P1 = D3 \oplus D5 \oplus D7 \oplus D9 \oplus D11$ = D9 ⊕ D10 ⊕ D11 ⊕ D12

one-bit errors, identify if there are one-bit errors and the location of the error bit. Suppose that the stored data is observed as 100111011111. Assuming that there can be only

[4 Marks

2 a 1 numbers when represented using the following methods. State the maximum and minimum numbers that can be represented by 10-bit binary Signed magnitude method.

H)

Two's complement method [1 Mark]

- 6 representing them as 6 bit binary numbers. Suppose that you have to carry out the binary multiplication 27  $\times$  -15 (not -15  $\times$  27) by [1 Mark]

- Evaluate is the two's complement representation of -15

11) Carry out the binary multiplication in the format given in Figure Q4.1 [1 Mark]

0 1

11) State the type of hazard associated with a wrong prediction of a branch instruction? State three pipeline hazards [1.5 Marks] [3 Marks]

E Explain what a program status word is?

[1 Mark]

[1 Mark]

- 0) 1) an equation for the speedup factor for N instructions. Assuming that each stage of a K-stage instruction pipeline is of duration T, derive

- ii) Calculate the maximum speedup that can be achieved due to the pipelining given in above part i)? [2 Marks]

[1 Mark]

Page 6 of 6