## **University of Ruhuna**

## Bachelor of Science (General) Degree Level II (Semester I) Examination September -2017

Subject: Physics

Course Unit: PHY 2112

## PART B - 01 hour & 15 minutes

Answer <u>FIVE</u> questions only.

All symbols have their usual meaning.

1.

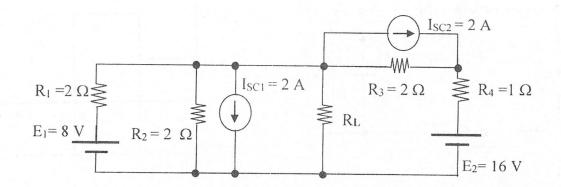

(a) Consider the circuit shown below.

i Using the source conversion calculate the thevenin's voltage across the R<sub>L</sub> [4 Marks]

ii What would be the maximum current passing through R<sub>L</sub>? [2 Marks]

iii What would be the value of RL in order to draw the maximum power from the circuit?

[1 Marks]

iv Calculate the maximum power drawn through the circuit by R<sub>L</sub>.

[1 Marks]

(b) Calculate the current (I<sub>L</sub>) passing through the load resister by using the Thevenin's theorem, in the circuit given below [2 Marks]

2. A capacitor of capacitance  $\mathbb{C}$  and a resistor (R) is connected in series with a battery of e.m.f.  $\mathbb{E}$  at time t = 0. The voltage across the capacitor,  $V_{\mathbb{C}}$ , as a function of time t is given by,

$$V_C = V_O e^{-\frac{t}{RC}} + E\left(1 - e^{-\frac{t}{RC}}\right)$$

Where: V<sub>O</sub> is the initial voltage of the capacitor

- (a) Sketch the variation of V<sub>C</sub> as function of time for the following cases.

- i  $0 \text{ V} < \text{V}_{\text{O}} < \text{E} \text{ and}$

[1 Marks]

[1 Marks]

ii  $0 V < E < V_O$

Figure A

Figure B

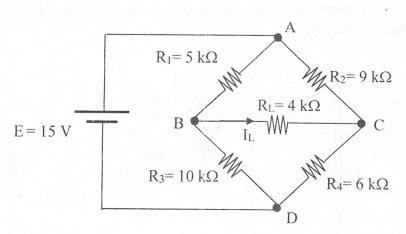

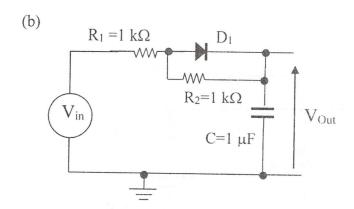

Time dependent input voltage ( $V_{in}$ ) shown in **figure B** is supplied to the circuit shown in **figure A**, which consists of two resistors, an ideal diode and an initially uncharged capacitor.

i Calculate the time constants for each voltage transitions

[1 Marks]

- ii Sketch the variation of the output voltage (Vout) as a function of time, t for the period 0 ≤ t ≤ 30 ms. (Assume that during each voltage transition capacitor stops the current conduction after a period of five time constants)

[4 Marks]

- iii If the diode R<sub>2</sub> is open-circuited due to a fault, redraw the function in part b (ii). [3 Marks]

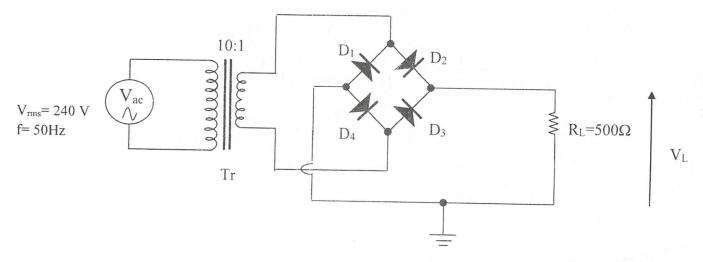

- 3. Answer the following parts considering the rectifier circuit given below. Neglect the resistance of the secondary winding of the transformer.

See the next page

(a) Calculate the followings (considering all diodes are ideal)

| ;   | Pools value of the h                                                 |              |

|-----|----------------------------------------------------------------------|--------------|

| 1   | Peak value of the voltage across R <sub>L</sub> ,                    | [3 Marks]    |

|     | rms value of the voltage across R <sub>L</sub> ,                     | [3 Marks]    |

|     |                                                                      | [1 Marks]    |

| iii | value of the d.c. component of the voltage across RL and             | [ Trital RS] |

| *** | value of the d.e. component of the voltage across R <sub>L</sub> and | [2 Marks]    |

| iv  | value of the a.c. component of the voltage across R <sub>1</sub>     |              |

| - ' | varies of the a.e. component of the voltage across R <sub>1</sub>    | [2 Markal    |

(b) If each diode has 0.7 V of forward bias voltage (V<sub>D0</sub>), calculate the followings by using the constant voltage drop model for diodes

| i  | Peak value of the voltage across R <sub>L</sub> , | [1 Monkal |

|----|---------------------------------------------------|-----------|

|    | Peak inverse voltage (PIV) of a diode             | [1 Marks] |

| 11 | reak inverse voltage (FIV) of a diode             | [1 Marks] |

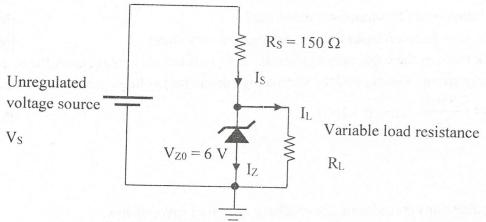

4. Consider the following zener diode shunt voltage regulator circuit.

This circuit is working under the following conditions

| Variable                                   | Minimum value | Maximum value |

|--------------------------------------------|---------------|---------------|

| Vs (unregulated voltage)                   | 12 V          | 24 V          |

| I <sub>L</sub> (current through the load ) | 2 mA          | 35 mA         |

- (a) Answer the following parts.

- i What is the desired regulated voltage across the load? [2 Marks]

- ii Assuming that this circuit operates as a voltage regulator, find the possible maximum and minimum current through the zener diode under the given conditions (use the constant voltage drop model for a zener diode).

[4 Marks]

- (b) If  $P_{z \text{ (max)}}$  is 750 mW and the minimum current ( $Iz_{min}$ ) of the zener diode to operate in the linear range is 2 mA,

- i is it possible to operate this circuit as a voltage regulator under the variations mentioned above?

ii What would be the impact on the zener diode, when the maximum value of the unregulated voltage supply (V<sub>S</sub>) is increased up to 50 V due to a fault?

[2 Marks]

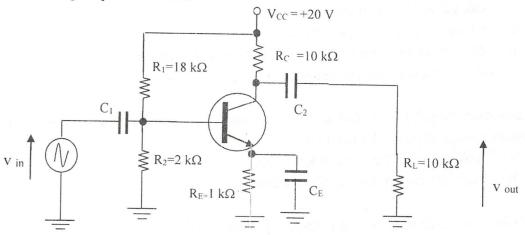

5. Consider the following amplifier circuit.

(a) What is the configuration of this transistor amplifier?

[Marks 2]

(b) Calculate  $I_{\text{E}}$  of the above circuit assuming  $I_{\text{B}}$  and  $V_{\text{BE}}$  are very small.

[Marks 3]

(c) Assuming the reactance of the capacitors against the ac signals are very small, draw the ac equivalent circuit for the above circuit. Hence, find the alternating current (ac) voltage gain (take emitter intrinsic

resistance,  $r_e' = \frac{25 \, mV}{I_E}$  and  $\beta = 100$ ). [Marks 5]

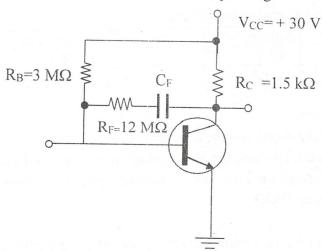

6. Answer the following questions considering the feedback amplifier given below.

(a) What is the form of the feed-back of this circuit?

[2 Marks]

(b) Calculate the following quantities. [ take  $r_e' = \frac{25 \, mV}{I_E}$ , common emitter current gain ( $\beta = 100$ ) and

V<sub>BE</sub> is very smaller value]

(i) Open-loop gain,

[4 Marks]

(ii) feed-back fraction and

[2 Marks]

(iii) closed-loop gain of the amplifier

[2 Marks]

(a) A logic circuit has three inputs (A, B, and C) and one output (Z). All input/output logic combinations of the circuit are shown in the following truth table,

| A | В | С   | Output<br>Z |

|---|---|-----|-------------|

| 0 | 0 | 0 . | 1           |

| 0 | 0 | 1   | 0           |

| 0 | 1 | 0   | 0           |

| 0 | 1 | 1   | 1           |

| 1 | 0 | 0   | 1           |

| 1 | 0 | 1   | 0           |

| 1 | 1 | 0   | 0           |

| 1 | 1 | 1   | 1           |

i Derive a logic expression for output signal (Z) as a logic function of inputs.

[2 Marks]

ii Simplify the logic expression obtained above.

[2 Marks]

- iii Construct a logic circuit by using the minimum number of 2-input NOR gates in order to implement the above logic expression. [3 Marks]

- (b) Simplify the following expression using a Karnaugh-Map (K-Map).

$$X = \overline{B}.\overline{C}.\overline{D} + \overline{A}.\overline{B}.C.\overline{D} + A.\overline{B}.C.\overline{D}$$

[3 Marks]